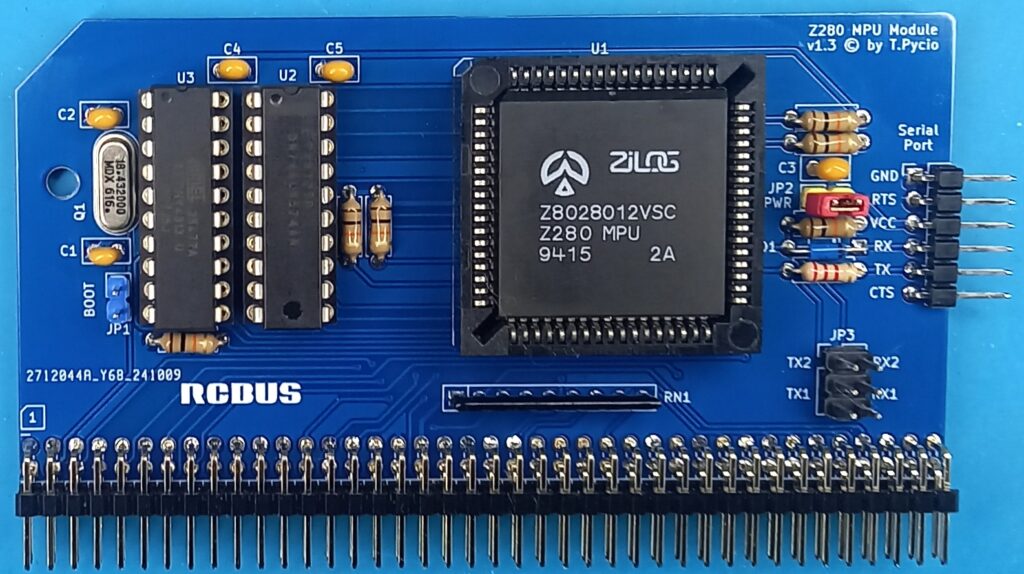

Moduł procesora Z280 wraz z mikrokontrolerem ATtiny4313 ustawiającym początkowe wartości rejestru sterującego (Bus Timing and Initialization Register) oraz generującym zegary na potrzeby CPU i układu transmisji szeregowej. Użycie mikrokontrolera uprościło budowę tego modułu i umożliwiło sterowanie, niedostępnym programowo, rejestrem BTIR w celu ustawienia zegara szyny oraz po zwarciu zworki JP1 BOOT wywołania trybu szeregowego ładowania wstępnego zawartością zawartą w pamięci EEPROM mikrokontrolera. Moduł w połączeniu z Memory Module 128-512kB tworzy system, w którym możliwe jest wykorzystanie obu trybów startu tego procesora (klasyczny z pamięcią ROM od adresu 0 oraz bootstrap wymagający pamięci RAM z adresem początkowym 0) dzięki możliwości przełączania mapowania ROM-RAM zworkami JP1-3 na module pamięci.

Lista elementów:

| Symbol | Ilość | Wartość/Oznaczenie |

|---|---|---|

| PCB | 1 szt. | PCB Z280 MPU v1.3 |

| U1 | 1 szt. | Z280 MPU (np. Z8028010VSC lub Z8028012VSC) |

| U2 | 1 szt. | 74HCT574 |

| U3 | 1 szt. | Mikrokontroler ATtiny4313A |

| Q1 | 1 szt. | Rezonator kwarcowy 18,432MHz |

| D1 | 1 szt. | Dioda przełączająca schottky np. BAT46, BAT85 |

| C1, C2 | 2 szt. | Kondensator ceramiczny/monolityczny 22pF raster 2,5mm |

| C3-C5 | 3 szt. | Kondensator ceramiczny/monolityczny 100nF raster 2,5mm |

| R1, R3-7 | 6 szt. | Rezystor 10k 1/4W |

| R2 | 1 szt. | Rezystor 2,2k 1/4W |

| RN1 | 1 szt. | Drabinka rezystorowa 8x10k SIP9 |

| JP1, JP2 | 2 szt. | 1×2 złącze szpilkowe „goldpin” raster 2,54 |

| JP3 | 1 szt. | 2×3 złącze szpilkowe „goldpin” raster 2,54 |

| P1 | 1 szt. | 1×6 asymetryczne złącze szpilkowe kątowe „goldpin” raster 2,54 |

| S1 | 1 szt. | 2×40 złącze szpilkowe kątowe „goldpin” raster 2,54 |

Schemat ideowy: