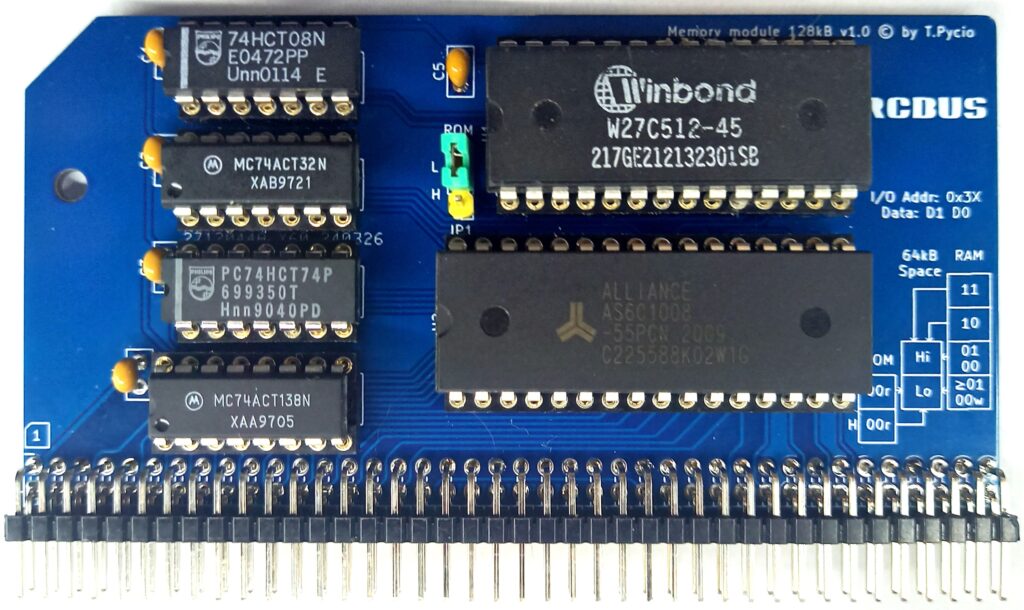

Moduł pamięci ROM 64kB, RAM 128kB zawierający prosty schemat przełączania 32kB banków pamięci. . Pamięć ROM ma możliwość wybrania dolnej lub górnej połówki za pomocą zworki JP1.

| D1 | D0 | Low 32kB | High 32kB |

|---|---|---|---|

| 0 | 0 | ROM* – JP1 | RAM 08000-0FFFF |

| 0 | 1 | RAM 00000-7FFFF | RAM 08000-0FFFF |

| 1 | 0 | RAM 00000-7FFFF | RAM 10000-17FFF |

| 1 | 1 | RAM 00000-7FFFF | RAM 80000-1FFFF |

* – Po RESET aktywna jest pamięć ROM do odczytu, jak również pamięć RAM w obszarze 00000-07FFFF dla zapisu. Taka funkcjonalność ułatwia wdrażanie nowych wersji BIOS bez żmudnego procesu programowania pamięci ROM.

Lista elementów:

| Symbol | Ilość | Wartość/Oznaczenie |

|---|---|---|

| PCB | 1 szt. | PCB Memory Module 128kB v.1.0 |

| U1 | 1 szt. | EPROM typu 27C512 |

| U2 | 1 szt. | Statyczna pamięć o organizacji 128kBx8 typu 628128 np. AS6C1008 |

| U3 | 1 szt. | 74HCT138 |

| U4 | 1 szt. | 74HCT74 |

| U5 | 1 szt. | 74HCT32 |

| U6 | 1 szt. | 74HCT08 |

| C1-C5 | 5 szt. | Kondensator ceramiczny/monolityczny 100nF raster 2,5mm |

| JP1 | 1 szt. | 1×2 złącze szpilkowe „goldpin” raster 2,54 |

| S1 | 1 szt. | 2×40 złącze szpilkowe kątowe „goldpin” raster 2,54 |

Schemat ideowy:

Dokumentacja projektu wraz plikami produkcyjnymi jest dostępna na Github